# Design and analyses of a low power linear voltage regulator in 0.18um CMOS process

Abstract. Linear voltage regulator is inevitable in most electronic systems and demands low power and low area. A low dropout (LDO) linear voltage regulator is proposed in this paper by utilizing Current Feedback Amplifier (CFA) technology. The design achieves low power and low area by reducing the internal compensation capacitor and resistors. The simulated result shows that the design consumes only 567.1370pW which is 35% less than the reference circuit. The design also achieves low area and higher gain.

Streszczenie. W artykule omówiono liniowy regulator napięcia wykorzystujący koncepcję LDO (low dropout). Układ wykorzystuje wzmacniacz z prądowym sprzężeniem zwrotnym CFA I technologię CMOS. Zrealizowano układ pobierający o 35% mniej energii niż układy znane z literatury. Projekt i analiza regulatora napięcia o małym poborze mocy wykonanego w technologii CMOS 0.18 µm

Keywords: CMOS, low dropout, voltage regulator.

Słowa kluczowe: regulator napięcia, low dropout, technologia CMOS

doi:10.12915/pe.2014.05.45

#### Introduction

System on Chip (SoC), modern communication systems including Wireless Local Area Network (WLAN), Radio Frequency Identification (RFID) etc are becoming increasingly popular day by day [1-4]. These systems demands low cost, high integrability and small size [5,6]. Power management is an essential device in these systems. Over-load protection, over-heat shield, stabilization, low power and low area are the essential features of the power management devices to assure the correct operation of these systems [7].

The rapid advancement of Complementary Metal Oxide Semiconductor (CMOS) technology allows management devices to achieve these criteria [8-10]. LDO linear voltage regulator is widely used in power management devices [11]. LDOs are one of the most critical modules as it is able to provide a nearly constant DC voltage for all the electronic systems. To regulate the performance (line and load regulation) transient overshoot and undershoot are required. On the other hand, to characterise, the power (output current, quiescent current, input and output voltage, and power and current efficiency) is necessary. Therefore, the LDOs need to be carefully designed to enhance the system stability in various operating condition.

LDOs contain the error amplifiers to detect the error between the output voltage and the reference. Error amplifier controls the pass transistor when the current passes through the output capacitor. Fast rejection of steep transient load variations, input voltage and loads are the metrics needed to be fulfilled when designing the LDO [12,13]. There are several methods to design the LDO such as pole-zero cancellation method, dual loop feedback and current-mode feedback buffer amplifier, voltage current source and flipped voltage follower to improve the stability and transient response [14-16]. Saberkari et al. proposed a current feedback amplifier for the fast transient response and regulation [17]. Dynamic biasing of derivative feedback was used in an ultra low power capless LDO by Jorge et al. [18]. Wang et al. improved the operating frequency by using the nested feedback loops in LDO linear voltage regulator [19]. However, none of the design could avoid numerous resistors and capacitors. A low power LDO linear voltage regulator is proposed in this paper by reducing the number of the resistors and capacitors by utilizing the CFA technology.

## Methodology

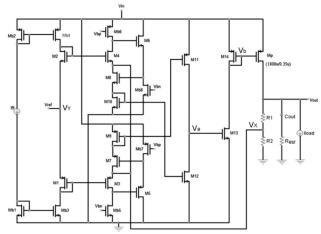

The proposed LDO linear voltage regulator is the modification of the [17] as shown in Fig. 1. The reference

circuit was built up using CFA topology. Open-loop voltage follower with output local current feedback based on a level-shifted slipped voltage follower (LSFVF) includes in CFA.

Fig.1. Reference circuit diagram [17]

The CFA consists of a pass transistor Mp, a class AB voltage follower M1-M12, an inverting output buffer (M13, M14). There are two feedback networks in that circuit which is R1 and R2. V<sub>ref</sub> is fed into the circuit to ensure no DC current drain. When load current increases, Vout is decreased. At the same time, the terminal voltage at M3, M4 and gate voltage M7, M8, M5 and M6 is also affected. The current passes through transistors (M7, M9, and M11) but the current is decreased at transistor M8, M10, M12. The voltage is increased at M13 but decreases at Mp.

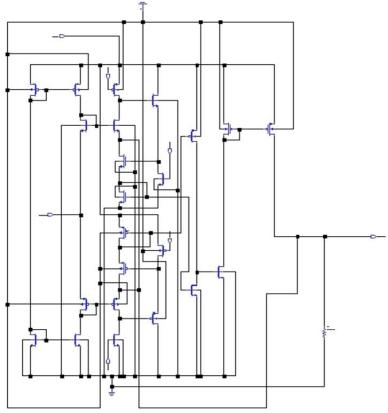

The proposed design reduces the complexity of the above mentioned circuit by reducing resistors and internal compensation capacitor. The schematic diagram of the proposed LDO linear voltage regulator is shown in Fig. 2. The parameters used for the proposed design are Resr= $2k\Omega$ , Vbp, Vbn and Vref=3V.

## **Result and Discussion**

The proposed voltage regulator was designed and simulated in 0.18- $\mu$ m CMOS process with the Design Architect (DA-IC) and IC station tools of Mentor graphics. The  $27^{0}$ C operating condition has been set for the reference LDO and the proposed LDO. The width and length of the transistors are shown in Table 1.

Fig.2. Schematic diagram of the proposed LDO linear voltage regulator

Table 1: Width and Length of the transistors

| Transistor            | Size (Width/Length)um |  |

|-----------------------|-----------------------|--|

| Mb2, Mb4, M2, Mb6, M4 | 7.5/0.25              |  |

| Mb1,M1, Mb3, M3, Mb5  | 15/0.25               |  |

| M8, M6, M11           | 1.4/0.25              |  |

| M10, M9, Mb7          | 0.5/0.18              |  |

| M7                    | 3.4/0.25              |  |

| Mb8                   | 1.65/0.25             |  |

| M5                    | 2.85/0.25             |  |

| M12                   | 1.4/0.18              |  |

| M14                   | 0.75/0.18             |  |

| M13                   | M13 0.1/0.25          |  |

| Мр                    | 50/0.18               |  |

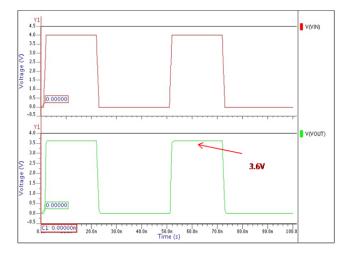

By using, the critical design parameters listed in Table 1, the output data V(out) for the modified LDO is shown in Fig.3 with supply voltage of 4 V. From Fig. 3 it is clear that, the output voltage is V(out) = 3.6 V after providing the 4V as the input voltage.

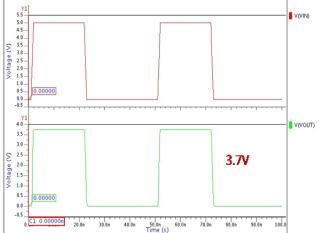

Figure 4 shows the V(out) when the input supply voltage is 5 V. However, the proposed LDO is able to produce 3.7V as the output voltage at this stage. The Vout before and after modification of the circuit is only 0.1V which does not differ much. Therefore, it is found that the design is sufficient enough to generate a good LDO regulated linear voltage output.

The gain between the reference LDO and the proposed LDO is compared to justify the better performance of the proposed design. Table 2 shows the comparison result of the gain between the reference circuit and the proposed circuit.

Fig. 3.Simulated output voltage with a 4V input voltage

Fig.4. Simulated output voltage with a 5V input voltage

Table 2. Comparison between the reference and proposed circuit

|         | [17]      |           | Proposed circuit |           |

|---------|-----------|-----------|------------------|-----------|

|         | Vin=4V,   | Vin=5V,   | Vin=4V,          | Vin=5V,   |

|         | Vout=2.8V | Vout=2.8V | Vout=3.6V        | Vout=3.7V |

| Gain    | 0.7       | 0.56      | 0.9              | 0.74      |

| Gain dB | -1.55     | -2.52     | -0.46            | -1.31     |

Based on the above result, the gain of the proposed circuit is better than the reference circuit. This is because the linear voltage regulator is a step-down converter. The proposed design also outperforms in power dissipation due to the reduction of resistors and capacitor. Table 3 shows the power dissipation of the proposed design with the reference circuit.

Table 3. Comparison of the power dissipation

|                                | [17]     | Proposed |

|--------------------------------|----------|----------|

| Power dissipation<br>(P Watts) | 867.1987 | 562.1370 |

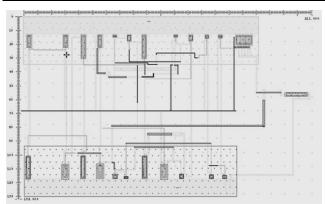

Fig. 5. Layout diagram of the proposed LDO voltage regulator

The usage of the resistors and capacitors increase the power dissipation. Based on Equation (1), chip junction temperature increases with the higher power dissipation.

$$(1) T_j = T_A + (R_{\theta \mathsf{IA}} x P_D)$$

where, PD is the power dissipation in package (W), TA is ambient temperature for the package (°C) and R  $\theta$ JA is junction to ambient thermal resistance (°C/W).

The layout of the proposed LDO linear voltage regulator was drawn with IC Station of Mentor Graphics as shown in Fig. 5. The transistors were drawn according to the calculated width and length of Table 1. The area of the proposed design was found only 311µm x 132µm.

## Conclusion

An improved LDO linear voltage regulator is presented in this paper. The modified circuit has been designed by using the CEDEC 0.18µm CMOS process. The design is capable of working under a voltage range from 4V to 5V. The power dissipation of the proposed design is only 562.1370pW which is 35% lower than the reference circuit. Additionally, the circuit is able to produce higher gain than the reference circuit. The design also achieves low area as the resistors and capacitor are avoided.

### **REFERENCES**

- [1] Mohd-Yasin F., Khaw M. K., Reaz M. B. I., Radio frequency identification: Evolution of transponder circuit design, *Microwave Journal*, 49(2006), 56-70.

- [2] Uddin J., Reaz M. B. I., Hasan M. A., Nordin A. N., Ibrahimy M. I., Ali M. A. M., UHF RFID antenna architectures and applications, *Scientific Research and Essays*, 5(2010), 1033-1051.

- [3] Rahman L. F., Reaz M. B. I., Ali M. A. Mohd., Kamada M., Design of an EEPROM in RFID tag: Employing mapped EPC

- and IPv6 address, in Proc. of the IEEE Asia-Pacific Conference on Circuits and Systems, (APCCAS 2010), 2010, 168-171.

- [4] Mohd-Yasin F., Khaw M. K., Reaz M. B. İ., Techniques of RFID systems: Architectures and applications, *Microwave Journal*, 49(2006), 62-74.

- [5] Amin M. S., Reaz M. B. I., Rahman L. F., Jalil J., Digital Modulator and Demodulator IC for RFID Tag Employing DSSS and Barker Code, *Journal of Applied Research and Technology*, vol. 10(2012), No. 6, 819-825,.

- [6] Amin M. S., Reaz M. B. I., Jalil J., Design of a novel adder-less Barker matched filter for RFID, *International Journal of Circuit Theory and Applications*, DOI: 10.1002/cta.1895, 2013.

- [7] Ho Q. T., Vo T. N., Nguyen H. D., Bui N. C., A current sensing circuit using current-voltage conversion for PMOS-based LDO regulators, in Proc. of the IEEE Symposium on Computer Applications and Industrial Electronics (ISCAIE), 2012, 1 – 4.

- [8] Teh Y. K., Mohd-Yasin F., Choong F., Reaz M. I., Kordesch A. V., Design and analysis of UHF micropower CMOS DTMOST rectifiers, *IEEE Transactions on Circuits and Systems II: Express Briefs*, 56(2009), 122-126.

- [9] Khaw M. K., Mohd-Yasin F., Reaz M. I., Recent advances in the integrated circuit design of RFID transponder, in Proc. Of the IEEE International Conference on Semiconductor Electronics (ICSE 2004), 2004, 326-330.

- [10] Romli N. B., Mamun M., Bhuiyan M. A. S., Husain H., Design of a Low Power Dissipation and Low Input Voltage Range Level Shifter in Cedec 0.18-µm Cmos Process, World Applied Sciences Journal, 19(2012), 1140-1148.

- [11] Rincon-Mora, G.A. and P.E. Allen, A low-voltage, low quiescent current, low dropout regulator, *IEEE Journal of Solid-State Circuits*, 33(1998), No. 1, 36-44.

- [12] Rincon-Mora G. A., Allen P. E., Optimized frequency-shaping circuit topologiesfor LDOs, *IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing*, 45(1998), No. 6, 703-708.

- [13] Heisley D., Wank B., DMOS delivers dramatic performance gains to LDO regulators. EDN, 45(2000), No. 13, 141-150.

- [14] Al-Shyoukh M., Hoi L., Perez R., A transient-enhanced low-quiescent current low-dropout regulator with buffer impedance attenuation, *IEEE Journal of Solid-State Circuits*, 42(2007), No. 8, 1732-1742.

- [15] Aziz F. I. B. A., Mamun M., Bhuiyan M. A. S., Bakar A. A. A., A Low Drop-Out Voltage Regulator in 0.18 µm CMOS Technology, *Modern Applied Science*, 7(2013), No. 4, 70-76.

- [16] Wonseok O., Bakkaloglu B., A CMOS low-dropout regulator with current-mode feedback buffer amplifier, IEEE Transactions on Circuits and Systems II: Express Briefs, 54(2007), No. 10, 922-926.

- [17] Saberkari A., Alarcón E., Shokouhi S. B., Fast transient current-steering CMOS LDO regulator based on current feedback amplifier, Integration, *The VLSI Journal*, 46(2013), No.2, 165-171.

- [18] Jorge E, João P., Júlio P., Marcelino S., Ultra low power capless LDO with dynamic biasing of derivative feedback, *Microelectronics Journal*, 44(2013), No.2, 94-102.

- [19] Wang C.-C., Kou R.-C., Tsai T.-H., A high precision low dropout regulator with nested feedback loops, *Microelectronics Journal*, 42(2011), No 7, 966-971.

Authors: Md. Syedul Amin, Department of Electrical, Electronic and Systems Engineering, Universiti Kebangsaan Malaysia, 43600 UKM, Bangi, Selangor, Malaysia, E-mail: <a href="mailto:syedul8585@yahoo.com">syedul8585@yahoo.com</a>; Lim Meng Rong, Department of Electrical, Electronic and Systems Engineering, Universiti Kebangsaan Malaysia, 43600 UKM, Bangi, Selangor, Malaysia, E-mail: <a href="mailto:mrfzmn@yahoo.com">mrfzmn@yahoo.com</a>;

Mamun Bin Ibne Reaz, Department of Electrical, Electronic and Systems Engineering, Universiti Kebangsaan Malaysia, 43600 UKM, Bangi, Selangor, Malaysia, E-mail: <a href="mamun.reaz@gmail.com">mamun.reaz@gmail.com</a>; Fazida Hanim Hashim, Department of Electrical, Electronic and Systems Engineering, Universiti Kebangsaan Malaysia, 43600 UKM, Bangi, Selangor, Malaysia, E-mail: <a href="fazida@eng.ukm.my">fazida@eng.ukm.my</a>; Noorfazila Kamal, Department of Electrical, Electronic and Systems Engineering, Universiti Kebangsaan Malaysia, 43600 UKM, Bangi, Selangor, Malaysia, E-mail: <a href="fazila@eng.ukm.my">fazila@eng.ukm.my</a>;

The correspondence address is: e-mail: syedul8585@yahoo.com