Electrical Engineering Department, College of Engineering, University of Hail, Hail 55211, Saudi Arabia

doi:10.15199/48.2024.02.51

# Design of a three-phase multilevel inverter using a SC cell for photovoltaic use

Abstract. In this study, a three-phase multilevel inverter (MLI) with low total harmonic distortion (THD) was developed, and it was found to be feasible by using a switched capacitor cell. Using just a single capacitor, a single DC supply, and nine switches, it can produce nine distinct inverter levels. The suggested inverter's gain and output voltage may need to be raised as the number of SC cells in use grows. Changing the input voltage's connection to the SC from series to parallel is accomplished by reversing the direction of electric charge flowing through the capacitor. The simulation results of the proposed model prove that 9-level inverter may be achieved using a single SC. The LTspice program was used to effectively compare the proposed topology to alternative, analogous MLI topologies. The proposed design is shown to lower total harmonic distortion (THD), while simultaneously using fewer components and a less complicated controller. The proposed inverter consumes less space and costs less because it uses fewer components. There were two types of loads used in this system: an ohmic load and an inductive ohmic load.

Streszczenie. W tym badaniu opracowano trójfazowy wielopoziomowy falownik (MLI) o niskim całkowitym zniekształceniu harmonicznym (THD), który okazał się wykonalny przy zastosowaniu przełączanego ogniwa kondensatora. Używając tylko jednego kondensatora, jednego źródła prądu stałego i dziewięciu przełączników, można wytworzyć dziewięć różnych poziomów falownika. W miarę wzrostu liczby używanych ogniw SC może zaistnieć potrzeba zwiększenia sugerowanego wzmocnienia falownika i napięcia wyjściowego. Zmiana połączenia napięcia wejściowego do SC z szeregowego na równoległe odbywa się poprzez odwrócenie kierunku ładunku elektrycznego przepływającego przez kondensator. Wyniki symulacji zaproponowanego modelu dowodzą, że przy użyciu jednego SC można uzyskać 9-poziomowy falownik. Do efektywnego porównania zaproponowanej topologii z alternatywnymi, analogicznymi topologiami MLI wykorzystano program LTspice. Wykazano, że proponowany projekt obniża całkowite zniekształcenia harmoniczne (THD), przy jednoczesnym wykorzystaniu mniejszej liczby komponentów i mniej skomplikowanego sterownika. Proponowany falownik zajmuje mniej miejsca i kosztuje mniej, ponieważ wykorzystuje mniej komponentów. W tym systemie zastosowano dwa rodzaje obciążeń: obciążenie omowe i obciążenie indukcyjne omowe. (Projekt trójfazowego falownika wielopoziomowego wykorzystującego ogniwo SC do zastosowań fotowoltaicznych)

**Keywords:** Photovoltaic PV system, three phase MLI inverter, switched-capacitor cells (SC), Full-Bridge-Switches (FBS). Słowa kluczowe: System fotowoltaiczny PV, trójfazowy falownik MLI, ogniwa z przełączanymi kondensatorami (SC), przełączniki pełnomostkowe (FBS).

#### Introduction

As one potential response to the problems facing the environment on a global scale, re-searchers have been concentrating their efforts on the creation of renewable energy sources. How-ever, renewable sources of energy are only capable of producing a small amount of power, which restricts the ways in which they may be exploited and implemented. It is only natural that as the output of renewable energy increases, so too will the number of ways in which it may be put to use. This is especially true in the burgeoning field of smart grids, as it is only natural that as the output of renewable energy increases, so too will the number of ways it can be put to use. The output of electrical systems can typically be increased with the help of step-up converters, invert-ers, and other similar devices. When using converters and inverters, respectively, the direction of energy transformation is from alternating current (AC) to direct current (DC) or from DC to AC. In order to complete this conversion process and achieve the high voltage output that is request-ed, it is necessary to make use of cumbersome magnetic devices such as transformers and inductors [1-3]. However, it has been demonstrated that the occupation of magnetic components results in a decrease in total efficiency. It is recommended that either the size of the magnetic elements be considerably reduced or that they be eliminated entirely in order to maintain a high level of overall efficiency in a number of different ways. This makes it possible to maintain a high degree of overall efficiency throughout the entire process [4]. There have been demonstrations of DC-to-DC switching capacitor (SC) converter designs that do not include magnetic components as presents in [5]. It is strongly advised to use non-isolated converters rather than DC-to-DC SC converters because non-isolated converters can achieve a better output gain and a higher power density than DC-to-DC SC converters.

There is also the potential to increase output gain by combining a non-isolated converter with a DC-to-DC SC converter [6-10]. Both of these potential courses of action could be successful.

SC converters are superior to other kinds of converters in terms of their ability to offer a higher voltage in an effective manner. The work that must be done by the SC cells in order to create an adequate amount of electric charge results in an increase in the input voltage. In order to reach its full potential, this type of stepped-up amplification makes use of charging and dis-charging capacitors that are arranged in parallel and series [5]. When capacitors are connected in parallel, the charging process can be sped up, but when capacitors are connected in series, the discharge period can be shortened. The correlation between voltage and the total number of capacitors contributes to a wide range of extra complications. In addition to that, a conversion from DC to DC was carried out with the help of the SC converters. Step-up considering that the dc link voltage is typically higher than the PV array voltage (which is typically in the range of hundreds of volts), DC to DC converters are commonly utilized in grid-connected PV systems. Off-grid PV inverters, PV inverters that can function either on or off the grid, and inverters pow-ered by a dc bus or battery are only some of the commercial inverters available to serve ac loads with a dc link voltage of 12 V to 70 V. Because PV modules are typically connected in series and parallel to form the array, the resulting voltage is typically higher than the nominal input voltage of the inverter (typically between 12 V and 70 V) and the nominal voltage of the battery (typically between 12 V and 70 V). So, in order to connect the PV array to the dc bus, step-down converters are necessary. On the other hand, a SC multilevel inverter (MLI) is the name given to the design of a DC-to-AC converter that is produced when SC cells are

paired with an inverter [11]. One of the most significant benefits of the MLI is its capacity to produce a higher AC voltage waveform, which may be accomplished without the utilization of a power transformer [12][13]. In addition to this, the multilayer SC three-phase inverter would call for a reduced number of switches and gate drivers to be utilized.

Other variations of the MLI have been created and implanted since O.C. Mak and A. loino-vici presented the initial MLI in 1998. In the early days of magnetic resonance imaging (MLI), researchers were primarily interested in discovering ways to lower total harmonic distortion (THD), improve inverter efficiency, and raise power density. One strategy for improving MLIs is referred to as "soft switching," and it plays a role in contributing to the system's ability to retain its overall efficiency even as it goes through transitions. The resonant technique is utilized by the majority of the suggested MLI systems due to the fact that it has been demonstrated to be beneficial in reducing switching loss and, as a result, enhancing inverter efficiency where most of which are modulated by PWM [14-17].

In both academic and industry settings, three phase MLIs have been widely used for high-power application investigations throughout the past two decades. These industries are interested in MLIs due to their high output voltages and low levels of harmonic distortion [18]. As a result, MLIs are becoming increasingly common in these settings. There are literally hundreds of distinct designs of three-phase inverters that can convert DC to AC at medium and high volt-ages [19-21]. Numerous applications exist for the ideas discussed here. Diode-attached, capacitorattached, and successive multilevel inverters (MLIs) are the three main types of MLIs. Among them, the diode-attached inverter is the most widely used. In this configuration, diodes play a crucial role in compressing DC voltage, leading to output voltage variations in a step-like manner. It's also believed that diodes enhance a circuit by making it more resistant to voltage fluctuations [13]. Power is supplied, and one or two diodes (represented by the notation n-1) are connected in series with the power source. In order to lower the THD and generate a sinusoidal waveform at the output voltage, more levels are required.

The topological designs that use clamped capacitors rather than diodes are the second most well-known type of MLI [17-21]. The three-phase MLI design incorporates capacitors, which al-low for a charging and discharging action that ultimately results in an increased input voltage. Altering the voltage supplied to flying capacitors is as simple as changing whether or not the capacitors are connected in series or parallel. It is possible for SC cells to have their input voltage amplified by utilizing certain topologies, such as the ladder design. The third type of MLI is called a cascade MLI, and it creates sinusoidal voltage by connecting a large number of Full-Bridge-Switches (FBS) inverters in a series configuration. The output voltage increases proportionally alongside the amount of inverter stages that are utilized. In comparison to the first two MLIs, the cascaded MLI has far less moving parts that need to be operational in order to function well. This is one of the most significant advantages of the cascaded MLI [22-26]. Clamped diodes and capacitors, which combine two or more of the earlier MLI kinds, have been employed to support the THD in cer-tain recent experiments. This technique, often referred to as the hybrid MLI, makes use of SC cells in a cascading form, and it has been implemented in a broad variety of other proposed models [11]. The goal of each of the SC cell topologies illustrated in these papers is to provide sup-port for the THD with the minimum number of components possible [27-28].

The proposed three-phase MLI aims to maximize output voltages while minimizing the number of components. Adding a SC cell to a three-phase FBS inverter not only boosts the inverter's voltage but also its output voltage. Instead of using twice as many input sources as in [29], the capacitor cell functions as adding another input voltage. Elevating the inverter output-level helps get a lower THD, which is ideal when trying to produce a sinusoidal output. Connected photovoltaic (PV) systems benefit from these varied inverter types. In order to verify the validity of the suggested model, the LTspice software was put to use. The evaluation of the proposed inverter in comparison to alternative designs that are conceptually identical demonstrated the usefulness of the project. This was proved by comparing the proposed design to the alternatives. The LTspice program was used to doublecheck the proposed model. [29-32].

# Th Proposed Topology

Compared to conventional MLIs, the proposed model can function with fewer parts per level. It is impossible to have both switches in the same leg switched ON at the same time without causing a disruption in the KVL and KCL of the proposed circuit. Doing so would result in a voltage short at the input, rendering the KVL useless. So, the features of the two switches that make up the same leg balance each other out. For each level of the proposed design, for instance, only five of the switches need to be active (ON) at once. This results in the 9L version of the architecture requiring nine switches. Lower (ON) switch counts help the proposed MLI achieve its goal of greater efficiency by reducing the losses associated with conduction and switching. As can be seen in Table 1, all nine possible switch states are used by all inverters. The AC line voltage at the output is 0 in one of the nine switching states shown in Table 1. This is true for at least one of the possible outcomes. Here, the AC line currents will freely cycle through either the higher or lower components. None of the other possibilities result in AC output line voltages of zero in the remaining states. To provide the required voltage waveform, the inverter will switch between states as needed. Because of this, the AC output line voltages that were generated include discrete values of ±2VDC, ±1.5VDC, ±1.0VDC, ±0.5VDC, and 0. Selecting which states to use to generate the required waveform is a critical part of the modulating strategy that guarantees the use of only the valid states. The purpose of this is to create the waveform. One prominent and commonplace use for three-phase FBS inverters is as an AC generator in applications like ac motor drives. Figure 5 explains the nine-step operating mode and how the output voltages are generated. The nine-step voltage divider (VSI) circuit is shown in Figure 1-a. The three phase voltages are generated by three bridges in this circuit, which are mutually phase-shifted by an angle of  $2\pi/3$ .

$$\begin{array}{l} \text{(1)}\ V_{aN} = \frac{2V_{in}}{\pi} \left[ cos\omega t - \frac{1}{3}cos\omega t + \frac{1}{5}cos\omega t - \frac{1}{7}cos\omega t + \cdots \dots \right. \\ \text{(2)}\ V_{bN} = \frac{2V_{in}}{\pi} \left[ cos(\omega t - 2\pi/3) - \frac{1}{3}cos(\omega t - 2\pi/3) + \frac{1}{5}cos(\omega t - 2\pi/3) - \frac{1}{7}cos(\omega t - 2\pi/3) + \cdots \dots \right. \\ \text{(3)}\ V_{cN} = \frac{2V_{in}}{\pi} \left[ cos(\omega t - 4\pi/3) - \frac{1}{3}cos(\omega t - 4\pi/3) + \frac{1}{5}cos(\omega t - 4\pi/3) - \frac{1}{7}cos(\omega t - 4\pi/3) + \cdots \dots \right. \\ \end{array}$$

In this case, the voltage across any two lines, Vac, is equal to the difference between their individual voltages, VaN and VcN which is  $\sqrt{3}$  times of the phase voltage.

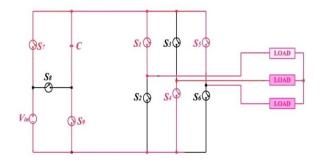

Fig.1. The proposed three phase nine level MLI supplied by a SC cell. b) switching time diagram of all switched of the proposed inverter.

Table 1. All switches and capacitor status for each output voltage level for the proposed MLI.

|                         |                |       |    |                |    |       | 9              |                | P P            |       |

|-------------------------|----------------|-------|----|----------------|----|-------|----------------|----------------|----------------|-------|

| Output Voltage<br>level | S <sub>1</sub> | $S_2$ | S₃ | S <sub>4</sub> | S₅ | $S_6$ | S <sub>7</sub> | S <sub>8</sub> | S <sub>9</sub> | O     |

| +2V <sub>in</sub> .     | 1              | 0     | 0  | 1              | 0  | 1     | 0              | 1              | 0              | Disch |

| +1.5 V <sub>in</sub>    | 1              | 0     | 0  | 1              | 0  | 0     | 0              | 1              | 0              | Disch |

| +1 V <sub>in</sub>      | 1              | 0     | 0  | 1              | 1  | 0     | 0              | 1              | 0              | Disch |

| 0.5 V <sub>in</sub>     | 1              | 0     | 0  | 1              | 1  | 0     | 1              | 0              | 1              | Ch    |

| 0                       | 1              | 1     | 0  | 1              | 1  | 0     | 1              | 0              | 1              | Ch    |

| -0.5V <sub>in</sub> .   | 0              | 1     | 1  | 0              | 0  | 1     | 1              | 0              | 1              | Ch    |

| -1 V <sub>in</sub>      | 0              | 1     | 1  | 0              | 0  | 1     | 0              | 1              | 0              | Disch |

| -1.5 V <sub>in</sub>    | 0              | 1     | 1  | 0              | 0  | 0     | 0              | 1              | 0              | Disch |

| -2V <sub>in</sub> .     | 0              | 1     | 1  | 0              | 1  | 0     | 0              | 1              | 0              | Disch |

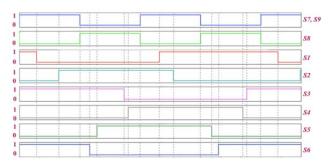

Fig.2. a) The proposed SC configuration combined with three phase FBS inverter to make up the three-phase, nine-MLI. b) parallel configuration between SC cell and three phase FBS-SC charging mode) c) series configuration between SC cell and three phase FBS-SC discharging mode).

#### The Series to Parallel SC cell

The SC cell functions as a supplementary voltage source in the suggested model. It takes just one capacitor and three switches to get a voltage boost equivalent to twice the input. A SC cell is the name given to this arrangement of switches and capacitor. Keep in mind that, as shown in (4), adding another SC cell will result in a rise in voltage, providing a generalization of the relationship between the SC and the output voltage.

$$(4) V_{out} = N * SC * V_{in}$$

Where N is the number of SC cell

Changing the voltage that is present at the terminals of the capacitor is one method that may be used to switch between the charging and discharging states that the capacitor is in. The parallel to series connection between the capacitors and the source is facilitated by applying a duty cycle of 50% percent to switches  $S_7$ ,  $S_8$ , and  $S_9$  respectively.

While linked in parallel to the input source when the capacitor is being charged, terminal C is connected in series to the source of power when the battery is being discharged. According to the charge equilibrium of the different modes of operation, the total charge of the series mode  $(Q_{series})$  must be equal to the total charge of the parallel mode  $(Q_{parallel})$  as shown in equation (5) [33-40].

$$Q_{series} = Q_{parallel}$$

The voltage across the capacitor ( $V_{SC}$ ) is identical to the input voltage ( $V_{in}$ ) when the circuit is in parallel mode (Figure 2-B), as shown in (6).

(6)

$$V_{SC} = V_{in}$$

Applying (7) is required to achieve (5)

(7)  $Q_{sertes} = CV_{SC}$  by substituting (5) for (6), we obtain (8).

$Q_{series} = V_{in}C$

When operating in series mode, as shown in Figure 2-C, the output voltage of a SC cell ( $V_{SCout}$ ) is calculated

byadding the input voltage to the voltage that is present across the capacitor (9).

$$(9) V_{SC} = V_{SCout} - V_{in}$$

This mode's total charge is shown in the following equati on (10).

(10)

$$Q_{parallel} = C(V_{SCout} - V_{in})$$

Returning to (5) and by equalizing (8) and (10) then (11)  $V_{out} = 2V_{in}$

### **Proposed MLI Configuration**

The proposed MLI topology includes a total of nine unidirectional switches and a single SC in its construction. The architecture of this particular inverter makes it possible to generate nine distinct voltage levels. When SC cell C is connected to  $V_{in}$  in parallel, it can attain a level of voltage balance that is comparable to the input voltage of Vin. At the same time, it is the duty of the DC input source Vin to bring the SC cell C up to a charged state. As soon as it has been loaded with charge, the storage capacitor C will be connected in series with the voltages that are being fed into the system so that it may serve as a supplementary source of power. Figure 3 reveals that the conductors S7, S8, and S9 are the ones who are responsible for creating the parallel and series connections between the Vin and the capacitor cell. These conductors are shown to be in charge of this responsibility. In the occasion, that switch S8 is turned on, the connection between Vin and C will be parallel. On the other hand, in the event that switches S7 and S9 are turned on, the connection between Vin and C will be series. Both the series and parallel connections will either supply the output with the exact same voltage as the input, or they will send twice as much voltage. Based on the switching time diagram presented in Figure 1-b, Table 1 outlines the states of the switches that must be operational to produce a three-phase 9L output voltage. These states are required in order to create the voltage.

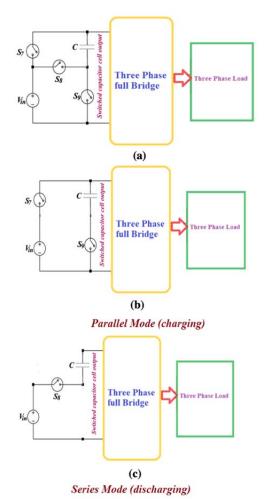

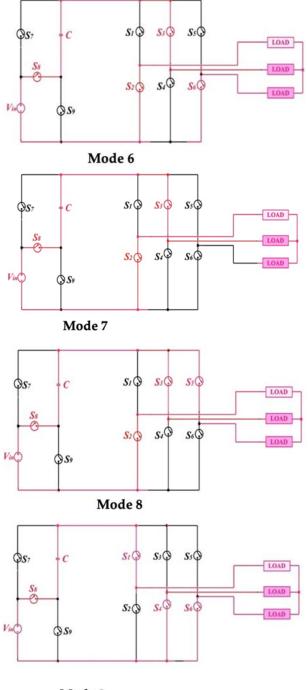

The concept of using multiple operating modes to provide varying voltage levels across a load. Nine distinct modes of operation for the SC-MLI have been proposed, and they are shown in Figure 3. These types of operation may be utilized in either positive or negative half-cycles depending on the state of switches. Table 1, which may be obtained through this link, provides an outline of the switching states for the proposed MLI. In the preceding table, we can see that a value of 0 indicates that the switches are in their "OFF" state, while a value of 1 indicates that they are in their "ON" state. The table clearly demonstrates that the SC cell C is either being charged or discharged, with the state "Ch" indicating charging and the state "Disch" indicating discharging. In the following paragraphs, we will talk about the many different output levels that the suggested three phase SC-MLI can provide.

The switches S1, S4, S5, S7, and S9 will result in the generation of ±0.5Vin . When capacitor C is connected in parallel with the DC input source, the voltage on it rises to Vin. When the input voltage is -1Vin, all of the switches S2, S3, S6, S7, and S9 are in the "ON" position. ±1 Vin voltage level: When the switches S1, S4, S5, and S8 are activated, a voltage of 1V is produced, as shown in Figure 3 (Mode 3) and (Mode 8). In a similar manner, discharging the capacitor C to the level of Vin requires putting it in series with the DC input source. the input voltage is deter-mined to be -1Vin when the state of switches S2, S3, S5, and S8 is (ON). Fiure 5 shows that in Mode 1, all of the switches S1, S4, S6, and S8 are in the "ON" position, which results in a voltage level of 2Vin. On the other hand, you may get a voltage level of -2Vin by activating the switches S2, S3, S5, and S8 (Figure 3, Mode 9). At these two levels, the SC C must be con-nected in series with the input source in order for C to function as an

extra voltage source. The voltage level of +1.5 Vin is the same as the voltage level of +2 Vin; however, an extra switch S6 is turned (ON), which results in a voltage drop and hence decreases the voltage level. The switch S2 is going to be activated so that the level may be lowered to -1.5Vin, which is a level that is lower than the level of -2Vin.

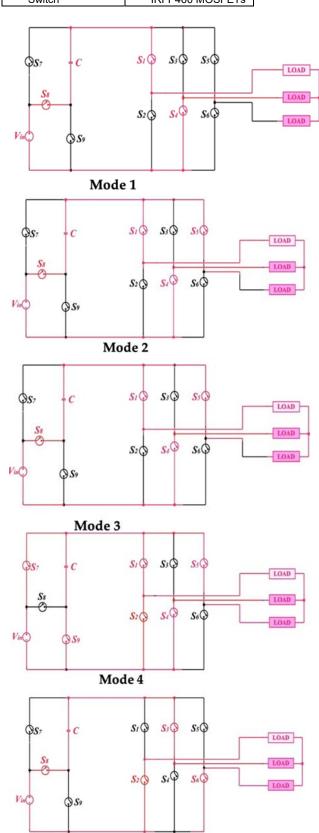

#### Simulated Results

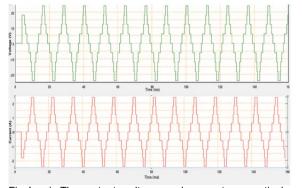

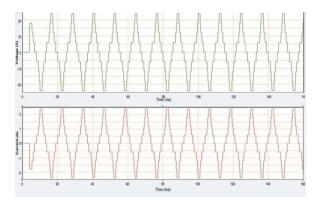

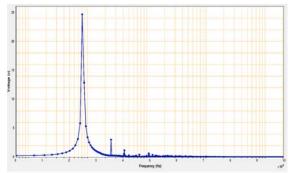

The simulations were run with the LTspice software. Simulation required the development of a three-phase 9L inverter, and its intended features are shown in Table 2. The proposed model was compared to several MLIs [29-32] to ensure its validity. We were able to actualize the possibility of extending the inverter levels with the installation of supplemental SC cells. Pulse-width modulation (PWM) was utilized to regulate the nine MOSFET switches at a switching frequency 100 kHz, and 50 Hz was selected as an output frequency of the proposed inverter. For the SC cell, which requires greater switching frequencies such as 100 kHz, MOSFETs are preferable over IBJTs to be used in the proposed inverter. In our simulations, we used an input voltage of 12V based on the PV battery, a resistive load of 100  $\Omega$ , an inductive load of 100  $\Omega$ , and a total inductance of 1mH. The waveforms of the output voltage and current appear in Figure 4 a) and b), respectively, when the selected frequency and modulation method are applied with simply a resistive load in use. The output waveforms of nine level inverters with minimal complexity switching are depicted clearly. Figure 5 shows the output when a resistive inductive load is used instead of the resistive load displayed in Figure 4. The current drawn from the power source rises when a resistive in-ductive load is also present. The suggested design includes SC cells, which provide input voltage to the whole three-phase FBS. When going from series to parallel SC operations, the input voltage varied widely, from 12V to 24V. The maximum output occurs at a voltage and current of 24 V and 2.5 A, respectively. From the input voltage, the output voltage is multiplied by two (Figure 4). This illustrates the practicality of the three phase SC-MLI. The THD must be analyzed since it is a fundamental characteristic that will be used to test the validity of the pro-posed layout. Without any filters, the output voltage's harmonic spectrum shows a THD value of 8.76 %, as seen in Figure 6. The results obtained are consistent with IEEE519 and other standards issued by the IEEE, the Institute of Electrical and Electronics Engineers. Simulations verified the existence of all nine levels, demonstrating their capacity to sustain inductive load and treble voltage gain. Capacitor C should be tuned to about 1 mF to provide a ripple-free voltage of less than 10%. Switches, diodes, capacitors, and dc power sources are counted and compared for how many individual parts they need. Table 3 provides a comprehensive comparison summary, from which it is clear that the suggested topology requires less components than the alternatives [29-32]. The benefits of MLI with a small number of components include decreased converter losses, a smaller footprint, and cheaper inverter costs. As shown in Table 3, we compared the proposed inverter to various MLI topologies in terms of total number of components, inverter gain, and total number of components per level. The primary abstract for all chosen references emphasizes in reducing the component amount of multilevel inverters.

Table 2. The simulation parameters.

| Parameter          | Value           |  |  |  |

|--------------------|-----------------|--|--|--|

| Supply Voltage (V) | 12V             |  |  |  |

| Supply frequency   | 50 Hz           |  |  |  |

| Carrier frequency  | 100 kHz         |  |  |  |

| Capacitor          | 1000 μF.        |  |  |  |

| Load               | 100 Ω , 1mH     |  |  |  |

| Switch             | IREP460 MOSEETs |  |  |  |

Mode 9

Fig.3. The proposed three-phase MLI may operate in one of nine different modes, each of which provides a different output voltage

Fig.4. a) The output voltage and current respectively of the proposed three phase MLI at resistive.

Mode 5

Fig.5. The output voltage and current respectively of the proposed three phase MLI at resistive inductive load.

Fig.6. T Illustration depicting the Total Harmonic Distortion (THD), visually represented by the harmonic spectrum observed in the

load voltage.

| Parameters                 | Proposed | Ref. [30] | Ref. [31] | Ref. [32] | Ref. [29] |

|----------------------------|----------|-----------|-----------|-----------|-----------|

| Number of levels           | 9        | 7         | 7         | 5         | 5         |

| Number of DC source        | 1        | 1         | 1         | 1         | 2         |

| Number of clamed diode     | 0        | 2         | 0         | 0         | 0         |

| Number of switches         | 9        | 10        | 10        | 9         | 10        |

| Number of capacitors       | 1        | 4         | 3         | 1         | 0         |

| Total components           | 10       | 16        | 13        | 10        | 10        |

| Total components per level | 1.11     | 2.28      | 1.85      | 2         | 2         |

| Inverter's Gain            | 2        | 1.5       | 3         | 2         | 1         |

#### **Conclusions**

This research successfully implemented a novel MLI architecture that makes use of less potent components. The proposed idea involves the intertwining of SC cells to produce an MLI without the need of any extra switches. The SC cells boost the inverter's input voltage and output levels using a series-to-parallel configuration. Both the output voltage and the total harmonic distortion (THD) are improved by the proposed models. An MLI model may be constructed for less money since fewer pieces are needed to provide the same amount of output at the higher level. According to this hypothesis, additional SC cells in the circuit might increase the output voltage and level of the proposed model. Both ohmic and inductive ohmic loads may benefit from the recommended design's low THD and low price.

# **REFERENCES**

- M. Norambuena, S. Kouro, S. Dieckerhoff, and J. Rodriguez, "Reduced Multilevel Converter: A Novel Multilevel Converter With a Reduced Number of Active Switches," IEEE Trans. Ind. Electron., vol. 65, no. 5, pp. 3636-3645, May. 2018.

- V Monteiro, JC Ferreira, AAN Meléndez, and J. L. Afonso, "Model predictive control applied to an improved five-level bidirectional converter," IEEE Trans. Ind. Electron., vol. 63, no. 9, pp. 5879-5890, Sept. 2016.

- 3 A. Alateeq, and M. Matin, "A Novel Design of a High Gain Stepup Converter Using Switched-Capacitors/Switched-Inductors Cells," in 2018 IEEE International Conference on Electro Information Technology (EIT), (in the Press).

- 4 B. Chen, W. Yao, and Z. Lu, "Novel five-level three-phase hybridclamped converter with reduced components," J. Power Electron., vol. 14, no. 6, pp. 1119-1129, Nov. 2014.

- M. D. Seeman and S. R. Sanders," Analysis and Optimization of Switched-Capacitor DC-DC Converters," in IEEE Transactions on Power Electronics, vol. 23, no. 2, pp. 841-851, March 2008.

- 6 A. Alateeq, Y. Almalaq and M. Matin," Using SiC MOSFET in switched-capacitor converter for high voltage applications," 2016 North American Power Symposium (NAPS), Denver, CO, 2016, pp. 1-5.

- 7 S. Xiong, S. C. Wong, S. C. Tan, and C. K. Tse, "A Family of Exponential Step-Down Switched-Capacitor Converters and

- Their Applications in Two-Stage Converters," *IEEE Trans. Power Electron.*, vol. 29, no. 4, pp. 1870–1880, 2014.

- 8 P. Pérez-Nicoli, P. C. Lisboa, F. Veirano, and F. Silveira, "A series-parallel switched capacitor step-up DC-DC converter and its gate-control circuits for over the supply rail switches," *Analog Integr. Circuits Signal Process.*, vol. 85, no. 1, pp. 37–45, 2015.

- 9 P. Pérez-Nicoli, P. C. Lisboa, F. Veirano, and F. Silveira, "A series-parallel switched capacitor step-up DC-DC converter and its gate-control circuits for over the supply rail switches," *Analog Integr. Circuits Signal Process.*, vol. 85, no. 1, pp. 37–45, 2015.

10

- Alateeq, Y. Almalaq, and M. Matin, A Performance of the Soft Charging Operation in Series of Step-Up Power Switched-Capacitor Converters, Journal of Low Power Electronics and Applications, vol. 8, no. 1, p. 8, Mar. 2018.

- 11 Alateeq, A.; Almalaq, Y.; Alateeq, A. Optimization of a Multilevel Inverter Design Used for Photovoltaic Systems under Variable Switching Controllers. *Processes* 2022, 10, 1159. https://doi.org/10.3390/pr10061159

- 12 P. A. Arbune and A. Gaikwad, "Comparative Study of Three level and five level Inverter", *International Journal of Advanced Research in Electrical Electronics and Instrumentation Engineering*, vol. 5, no. 2, pp. 681-686, Feb 2016.

- 13 J. Rodriguez, J. S. Lai and F. Z. Peng, "Multilevel inverters: a survey of topologies controls and applications", *IEEE Transactions on industrial electronics*, vol. 49, no. 4, pp. 724-738, Nov 2002.

- 14 Ramos-Paja, C.A.; Bastidas-Rodriguez, J.D.; Saavedra-Montes, A.J. Low-Voltage Photovoltaic System Based on a Continuous Input/Output Current Converter. Computation 2023, 11, 42. https://doi.org/10.3390/computation11020042

15

- Khemili, F.Z.; Bouhali, O.; Lefouili, M.; Chaib, L.; El-Fergany, A.A.; Agwa, A.M. Design of Cascaded Multilevel Inverter and Enhanced MPPT Method for Large-Scale Photovoltaic System Integration. Sustainability 2023, 15, https://doi.org/10.3390/su15129633

- 16 M. Jayabalan, B. Jeevarathinam and T. Sandirasegarane, "Reduced switch count pulse width modulated multilevel inverter," in IET Power Electronics, vol. 10, no. 1, pp. 10-17, 2017.

17

- N. Motaparthiand and K. Malligunta, " Seven-Level Symmetrical Series/Parallel Multilevel Inverter with PWM Technique Using Digital Logic," International Journal of Electrical and Computer Engineering Systems (IJECES), vol. 12, no. 3, pp. 123-130, 2021.

- 18 E. Najafi and A. H. Yatim, "Design and implementation of a new multilevel inverter topology", *IEEE Transactions on Industrial Electronics*, vol. 59, no. 11, pp. 4148-4154, Nov 2011.

- 19 J. J. Nedumgatt, D. V. Kumar, A. Kirubakaran and S. A. Umashankar, "multilevel inverter with reduced number of switches", 2012 IEEE Students' Conference on Electrical Electronics and Computer Science, pp. 1-4, 2012 Mar 1.

- 20 K. Ramani, M.A. Sathik, S Sivakumar, " A New Symmetric Multilevel Inverter Topology Using Single and Double Source Sub-Multilevel Inverters", Journal of Power Electronics, Volume 15, Issue 1, 2015, pp.96-105.

- 21 V. Thiyagarajan and P. Somasundaram, "A New Seven Level Symmetrical Inverter with Reduced Switch Count", International Journal of Power Electronics and Drive System (IJPEDS), vo9, no. 2, pp. 921-925, 2018.

- 22 T. T. Tran, and M. K. Nguyen "Cascaded five-level quasi-switchedboost inverter for single-phase grid-connected system," IET Power Electron., vol. 10, no. 14, pp. 1896-1903, Nov. 2017.

- 23 M. K. Nguyen, & T. T. Tran, "Quasi cascaded H-bridge five-level boost inverter," IEEE Trans. Ind. Electron.," vol. 64, no. 11, pp. 8525-8533, Nov. 2017.

- 24 E. Babaei, S. Laali and Z. Bayat, "A single-phase cascaded multilevel inverter based on a new basic unit with reduced number of power switches", *IEEE Transactions on industrial* electronics, vol. 62, no. 2, pp. 922-929, Jul 2014.

- 25 Y Hu, Y Xie, L Cheng, and D Fu., "Characteristics analysis of a new single-phase  $\pi$ -type five-level inverter," IET Power Electron., vol. 9, no. 6, pp. 1290-1296. May. 2016.

- 26 A. V. Ho, & T. W. Chun, "Single-Phase Modified Quasi-Z-Source Cascaded Hybrid Five-Level Inverter," IEEE Trans. Ind. Electron., vol. 65, no. 6, pp. 5125-5134, Jun. 2018

- 27 Piccini, A.R.; Guimarães, G.C.; Souza, A.C.d.; Denardi, A.M. Implementation of a Photovoltaic Inverter with Modified Automatic Voltage Regulator Control Designed to Mitigate Momentary Voltage Dip. Energies 2021, 14, 6244. https://doi.org/10.3390/en14196244

- 28 Chung, D.D.L. First Review of Conductive Electrets for Low-Power Electronics. J. Low Power Electron. Appl. 2023, 13, 25. https://doi.org/10.3390/jlpea13020025

- 29 Karasani, R.R.; Borghate, V.B.; Meshram, P.M.; Suryawanshi, H.M.; Sabyasachi, S. A Three-Phase Hybrid Cascaded Modular

- 30 Multilevel Inverter for Renewable Energy Environment. IEEE Trans. Power Electron. 2017, 32, 1070–1087

- 31 Lee, S.S.; Bak, S.Y.; Kim, A.; Joseph, M.; Lee, K.B. New Family of Boost Switched-Capacitor Seven-Level Inverters (BSC7LI). IEEE Trans. Power Electron. 2019, 34, 10471– 10479

- 32 Sathik, M.J.; Sandeep, N.; Blaabjerg, F. High Gain Active Neutral Point Clamped Seven-Level Self-Voltage Balancing Inverter. IEEE Trans. Circuits Syst. II Express Briefs 2020, 67, 2567–2571

- 33 Sandeep, N.; Ali, J.S.M.; Yaragatti, U.R.; Vijayakumar, K. A Self-Balancing Five-Level Boosting InverterWith Reduced Components. IEEE Trans. Power Electron. 2019, 34, 6020– 6024